- 您现在的位置:买卖IC网 > Sheet目录299 > 71M6545-IGT/F (Maxim Integrated)IC ENERGY METERING

�� �

�

�

�71M6545/71M6545H� Data� Sheet�

�The� page� erase� sequence� is:�

�?�

�?�

�Write� the� page� address� to� FLSH_PGADR[6:0]� (� SFR� 0xB7[7:1])� .�

�Write� the� pattern� 0x55� to� the� FLSH_ERASE� register� (� SFR� 0x94� ).�

�Program Security�

�When� enabled,� the� security� feature� limits� the� ICE� to� global� flash� erase� operations� only.� All� other� ICE�

�operations,� such� as� reading� via� the� SPI� or� ICE� port,� are� blocked.� This� guarantees� the� security� of� the� user’s�

�MPU� and� CE� program� code.� Security� is� enabled� by� MPU� code� that� is� executed� in� a� 64� CKMPU� cycle�

�pre-boot� interval� before� the� primary� boot� sequence� begins.� Once� security� is� enabled,� the� only� way� to�

�disable� it� is� to� perform� a� global� erase� of� the� flash,� followed� by� a� chip� reset.�

�The� first� 64� cycles� of� the� MPU� boot� code� are� called� the� pre-boot� phase� because� during� this� phase� the�

�ICE� is� inhibited.� A� read-only� status� bit,� PREBOOT� (SFR� 0xB2[7])� ,� identifies� these� cycles� to� the� MPU.�

�Upon� completion� of� pre-boot,� the� ICE� can� be� enabled� and� is� permitted� to� take� control� of� the� MPU.�

�The� security� enable� bit,� SECURE� (SFR� 0xB2[6])� ,� is� reset� whenever� the� chip� is� reset.� Hardware� associated�

�with� the� bit� allows� only� ones� to� be� written� to� it.� Thus,� pre-boot� code� may� set� SECURE� to� enable� the� security�

�feature� but� may� not� reset� it.� Once� SECURE� is� set,� the� pre-boot� and� CE� code� are� protected� from� erasure,�

�and� no� external� read� of� program� code� is� possible.�

�Specifically,� when� the� SECURE� bit� is� set,� the� following� applies:�

�?�

�?�

�?�

�The� ICE� is� limited� to� bulk� flash� erase� only.�

�Page� zero� of� flash� memory,� the� preferred� location� for� the� user’s� pre-boot� code,� may� not� be�

�page-erased� by� either� MPU� or� ICE.� Page� zero� may� only� be� erased� with� global� flash� erase.�

�Write� operations� to� page� zero,� whether� by� MPU� or� ICE� are� inhibited.�

�The� 71M6545/H� also� includes� hardware� to� protect� against� unintentional� Flash� write� and� erase.� To� enable�

�flash� write� and� erase� operations,� a� 4-bit� hardware� key� that� must� be� written� to� the� FLSH_UNLOCK[3:0]� field.�

�The� key� is� the� binary� number� ‘0010’.� If� FLSH_UNLOCK[3:0]� is� not� ‘0010’,� the� Flash� erase� and� write� operation�

�is� inhibited� by� hardware.� Proper� operation� of� this� security� key� requires� that� there� be� no� firmware� function� that�

�writes� ‘0010’� to� FLSH_UNLOCK[3:0]� .� The� key� should� be� written� by� the� external� SPI� master,� in� the� case� of�

�SPI� flash� programming� (SFM� mode),� or� through� the� ICE� interface� in� the� case� of� ICE� flash� programming.�

�When� a� boot� loader� is� used,� the� key� should� be� sent� to� the� boot� load� code� which� then� writes� it� to�

�FLSH_UNLOCK[3:0].� FLSH_UNLOCK[3:0]� is� not� automatically� reset.� It� should� be� cleared� when� the� SPI� or�

�ICE� has� finished� changing� the� Flash.� Table� 38� summarizes� the� I/O� RAM� registers� used� for� flash� security.�

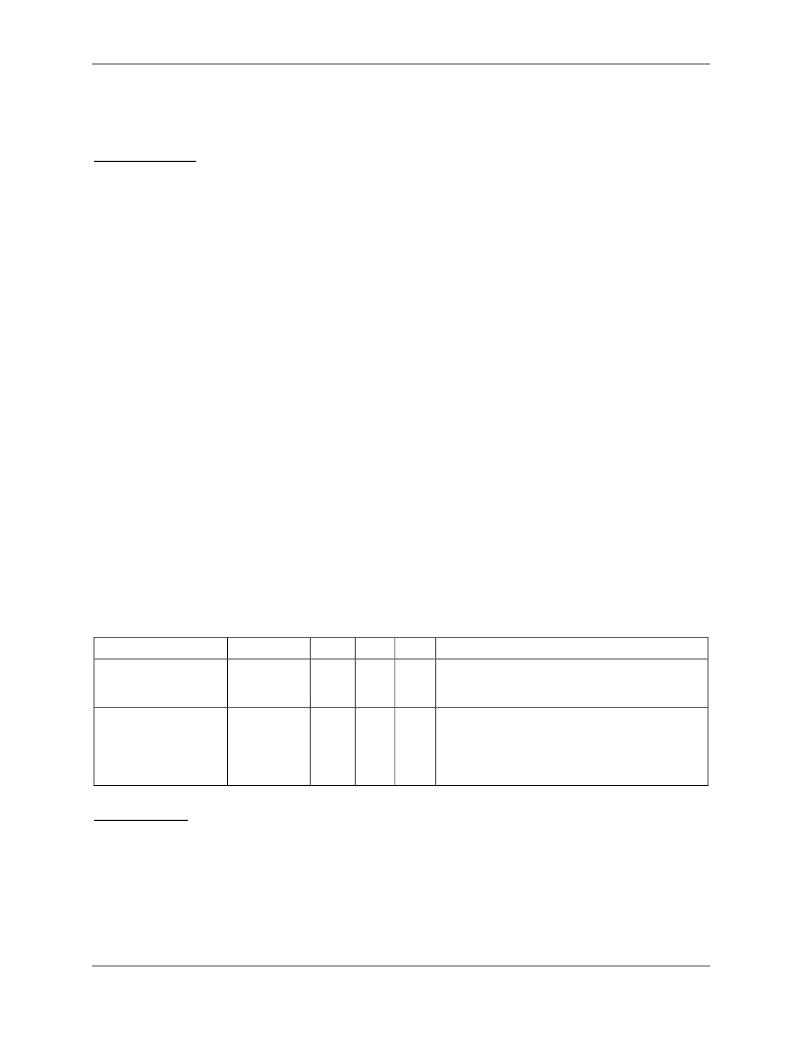

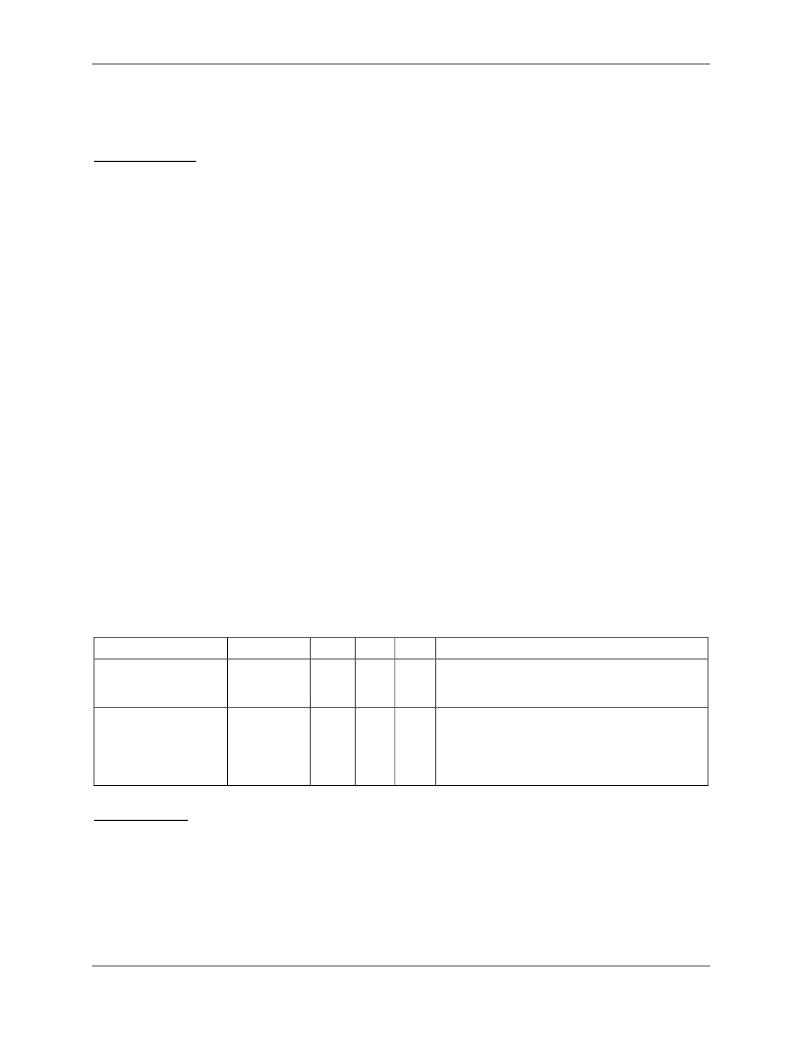

�Table� 38:� Flash� Security�

�Name�

�FLSH_UNLOCK[3:0]�

�SECURE�

�Location�

�2702[7:4]�

�SFR� B2[6]�

�Rst�

�0�

�0�

�Wk�

�0�

�0�

�Dir�

�R/W�

�R/W�

�Description�

�Must� be� a� 2� to� enable� any� flash� modification.�

�See� the� description� of� Flash� security� for�

�more� details.�

�Inhibits� erasure� of� page� 0� and� flash� addresses�

�above� the� beginning� of� CE� code� as� defined�

�by� CE_LCTN[5:0� ](I/O� RAM� 0x2109[5:0]).�

�Also� inhibits� the� read� of� flash� via� the� ICE�

�and� SPI� ports.�

�SPI Flash Mode�

�In� normal� operation,� the� SPI� slave� interface� cannot� read� or� write� the� flash� memory.� However,� the�

�71M6545/H� contains� a� Special� Flash� Mode� (SFM)� that� facilitates� initial� (production)� programming� of� the�

�flash� memory.� When� the� 71M6545/H� is� in� SFM� mode,� the� SPI� interface� can� erase,� read,� and� write� the�

�flash.� Other� memory� elements� such� as� XRAM� and� I/O� RAM� are� not� accessible� to� the� SPI� in� this� mode.�

�In� order� to� protect� the� flash� contents,� several� operations� are� required� before� the� SFM� mode� is� successfully�

�invoked.�

�v2�

�47�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

720-10007-00300

CBL D-SUB 9PIN FMAL-25PIN FML 3M

720-10010-00025

CBL DSUB 9PIN FML-25PIN MAL .25M

720-10020-00300

CBL DSUB 9PIN FML-9PIN MALE 3M

720-10021-00300

CBL DSUB 9PIN FML-9PIN FEMAL 3M

72231-0881

8 POS T/P SHLD 4 GR ASSY

7250B

PANEL KIT BOTTOM FOR R-1220 CASE

731-10061-00200

CBL DSUB HD 15FEMAL-15MALE 2.0M

73304-111

MJ HOR ESMT 8/8 H/O T&R

相关代理商/技术参数

71M6545-IGTR/F

功能描述:计量片上系统 - SoC Metrology Proc. (3P 64K Flsh .1%)

RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel

71M6545T-IGT/F

制造商:Maxim Integrated Products 功能描述:METROLOGY PROCESSORS - Rail/Tube

71M6545T-IGTR/F

制造商:Maxim Integrated Products 功能描述:3-PHASE AFE, 32KB FLASH, PRES TEMP SENSOR - Tape and Reel

71M6601

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:On-Chip Temperature Sensor Enables Localized Digital Temperature On-Chip Power Monitoring

71M6601-IF

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:On-Chip Temperature Sensor Enables Localized Digital Temperature On-Chip Power Monitoring

71M6601-IL

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:On-Chip Temperature Sensor Enables Localized Digital Temperature On-Chip Power Monitoring

71M6601-IL/F

功能描述:模数转换器 - ADC Isolated Sensor IC

RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

71M6601-ILF

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:On-Chip Temperature Sensor Enables Localized Digital Temperature On-Chip Power Monitoring